# Open-Source Analog Design Flow Using Efabless and the SkyWater 130 nm PDK

Documentation Created By: Joshua Thater Information Current as of 11/27/2023

## **Table of Contents**

| Table of Contents.         Preamble/Introduction.                |    |

|------------------------------------------------------------------|----|

| Guide to Setting up a Virtual Environment for Analog Design Flow |    |

| Guide to Setting up Tool Environment for Analog Design Flow      |    |

| Required Packages                                                |    |

| Magic VLSI                                                       | 12 |

| Xschem                                                           | 15 |

| Ngspice                                                          | 17 |

| GAW (optional)                                                   | 19 |

| Netgen                                                           | 21 |

| Open PDKs Install                                                | 23 |

| Tool Usage + Example "Hello World" Type Project                  | 25 |

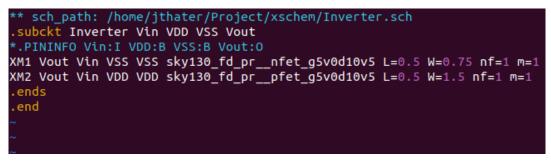

| Schematic Capture/Creation + Simulation                          | 27 |

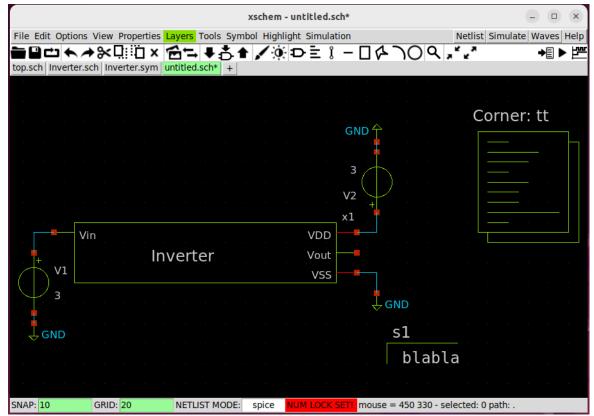

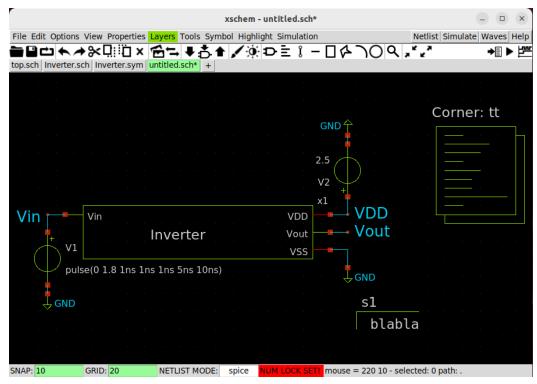

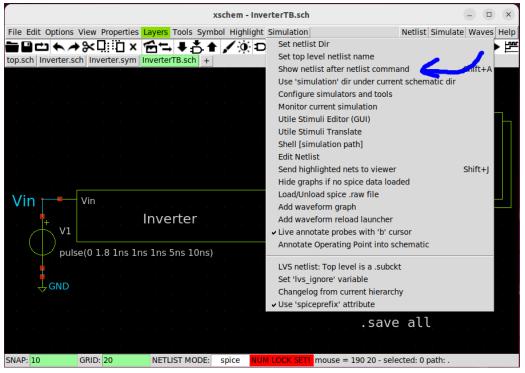

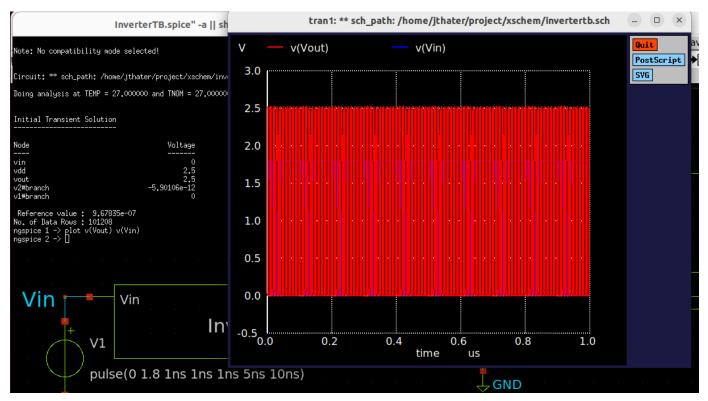

| Example Inverter Schematic Creation and Simulation               | 29 |

| Layout Creation + DRC/LVS                                        |    |

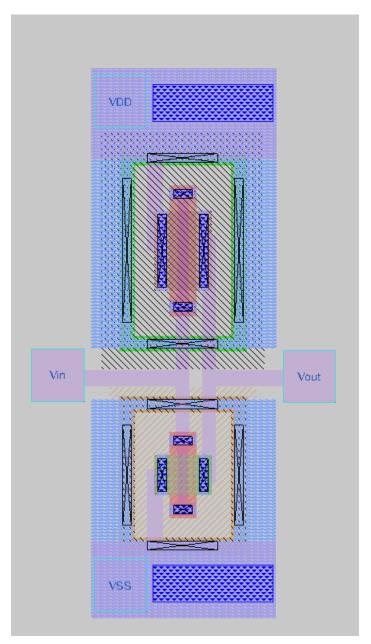

| Example Inverter Layout + LVS                                    |    |

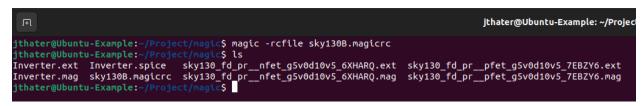

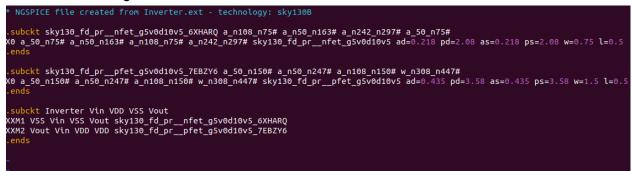

| Parasitic Netlist Extraction + Post-Layout Simulation            | 60 |

| Example Inverter R+C Extraction + Post-Layout Simulation         | 60 |

| Integration of Design with Harness Through Efabless              | 66 |

| Example Inverter Harness Hookup                                  |    |

| BONUS: ReRAM Setup                                               | 78 |

## **Preamble/Introduction**

This guide aims to teach the open-source analog design flow integrating with Efabless. This process is currently not well documented and is very complicated for beginners. This guide will hopefully try to remedy that.

Analog design is complicated enough with commercial tools, but it becomes even more complicated with open-source tools. With Cadence, we are able to do all steps of the analog design flow in one tool. However, in the open-source design flow, there is a tool for each step of the process. The core design flow for open-source analog design is as follows:

- 1. Schematic Capture/Creation (Tools: Xschem)

- 2. Simulation of Schematic (Tools: Ngspice, Xspice, Xyce)

- 3. Layout Creation (Tools Magic, Klayout)

- 4. LVS check (Tool: Netgen)

- 5. Post-Layout Simulations (Tool: Xschem & Ngspice/Xyce)

These are the tools that allow for open-source analog design, but you will still need a library/PDK so that you have devices to create your components and rule sets to follow in layout. This is where Open PDKs come in handy. Open PDKs define a standard set of libraries and files that will allow you to design circuits using a PDK. Open PDKs mainly support two PDKs - the SkyWater 130 nm process and the GF180MCU process. This guide will cover the setup and rules for the SkyWater 130 nm process, but the GF180MCU process should also work - albeit with slightly different rules.

This guide will try to be as explanatory as possible on all aspects of the open-source analog design flow - including a very detailed walkthrough example. As a result, this guide will be very long and perhaps a little long-winded in some places. However, my goal with this guide is to ensure that you have a solid understanding of the tools, the analog design flow, and how everything fits together so that you can focus on your designs - instead of everything leading up to them. This guide is also very beginner-friendly, so a lot of basic commands will be shown. This is so that people with little to no terminal experience can still learn to install and use these tools.

In this guide, I will detail what has worked for our team and try to show alternatives when available. I will also try my best to link out to outside sources, other documents, and other tutorials as well. However, this guide will try and centralize all of this information into one place. I hope that you find this guide helpful, and I also hope that you continue to add and edit this guide for future teams.

One final note: please join this Slack channel and don't be afraid to ask questions, as there are very smart people in there: https://open-source-silicon.dev

# Guide to Setting up a Virtual Environment for Analog Design Flow

This will provide a general guide on how to set up a virtual environment that will be able to house all the tools that are needed for the open-source analog design flow.

To start things things off, in order to do the analog design flow, it is *heavily recommended* to use a Linux system or MAC system. It may be possible to use a Windows operating system, but certain software may be out of date or not available at all.

#### <u>This entire guide will assume you are using a Linux system - specifically an</u> <u>Ubuntu system.</u>

I recommend using a VM running Ubuntu since, in my experience, it is the easiest to work with, and it is what my team has been using during our time working on our senior design project. If you have another preference, go with that, but just remember that this guide is specifically made for people using an Ubuntu system. So, you might have to run different commands, tweak different settings, and set up other dependencies to get things working.

The rest of this section will cover how to download and install a Ubuntu VM with the specific hardware requirements needed for this analog design flow. If you do not plan to use an Ubuntu VM for your environment, then you can safely skip this section. However, be sure that your environment will be able to run all the tools that are needed.

I recommend using Virtual Box for your VM. Below is the link to download Virtual Box: <u>https://www.virtualbox.org/wiki/Downloads</u>

Once you have Virtual Box downloaded, it is time to set up the Ubuntu VM. First, head to the webpage linked below. Ubuntu Desktop Virtual Machine Set Up: <u>https://ubuntu.com/download/desktop</u>

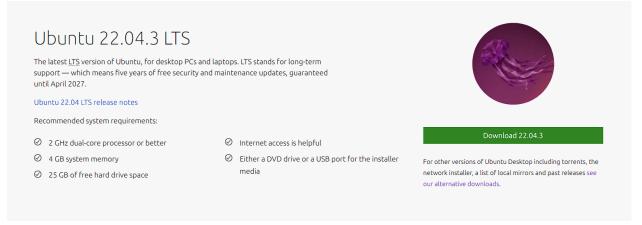

Once there, download an Ubuntu image. It shouldn't matter which one you choose; just make sure it is past Ubuntu 20 (which all of them on the download page should be anyway). For this example, I will be using Ubuntu 22.04.3, which can be seen below.

#### Figure 1: Ubuntu Image

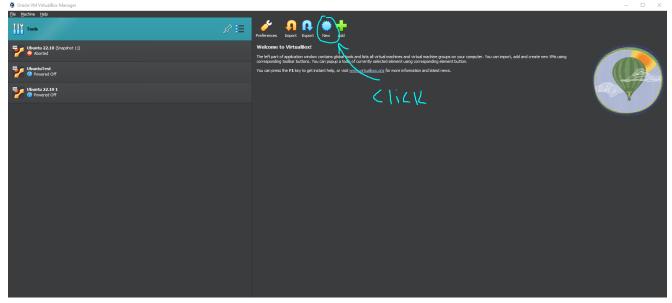

This ISO is a few GB, so it may take a bit to install. Once it is installed, you can head over to Virtual Box. Once in Virtual Box, you should see a screen similar to the one seen below (you will not see the VMs that I currently have set up). To begin setting up the virtual machine, click on "New" as seen in the figure below.

Figure 2: Virtual Box Setup

Once that is done, simply give a name to your virtual machine and select the ISO image you just downloaded (the ISO should be in your downloads directory). If you did all that correctly, it should look something like this.

#### Create Virtual Machine

| 🤴 Create Virtual Machi | ine                |                                                                                                                                                                                                          | ?            | ×        |  |  |  |  |

|------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------|--|--|--|--|

|                        | Virtual            | machine Name and Operating System                                                                                                                                                                        |              |          |  |  |  |  |

|                        | used throug        | se a descriptive name and destination folder for the new virtual machine. The name you hout VirtualBox to identify this machine. Additionally, you can select an ISO image which guest operating system. |              |          |  |  |  |  |

|                        | <u>N</u> ame:      | Ubuntu_Example                                                                                                                                                                                           |              | <b>~</b> |  |  |  |  |

|                        | <u>F</u> older:    | C:\Users\Josh\VirtualBox VMs                                                                                                                                                                             |              |          |  |  |  |  |

|                        | <u>I</u> SO Image: | C: \Users \Josh \Downloads \ubuntu-22.04.3-desktop-amd64.iso                                                                                                                                             |              |          |  |  |  |  |

|                        | <u>E</u> dition:   |                                                                                                                                                                                                          |              |          |  |  |  |  |

|                        | <u>T</u> ype:      |                                                                                                                                                                                                          |              | 64       |  |  |  |  |

|                        | Version:           |                                                                                                                                                                                                          |              | _        |  |  |  |  |

|                        |                    | Skip Unattended Installation                                                                                                                                                                             |              |          |  |  |  |  |

|                        |                    | Detected OS type: Ubuntu (64-bit). This OS type can be installed unattendedly. The<br>start after this wizard is dosed.                                                                                  | install v    | vill     |  |  |  |  |

| Help                   |                    | Expert Mode Back Next                                                                                                                                                                                    | <u>C</u> ano | el       |  |  |  |  |

Figure 3: VM Name

Once this is done, click next. On the following screen, you can change the username and password of your machine. It is recommended that you change these settings so that you can get sudo access on your machine. I would not worry about changing the hostname or domain name. Finally, on this screen, make sure to select the box for "Guest Additions"; this adds a bunch of quality-of-life features, such as dynamic screen resolution. Once this is all done, it should look something like this.

| 🤴 Create Virtual Machin | e                            |                                                                                                                                                                                                                                   |               |                      |                       | ?             | $\times$ |  |  |

|-------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------|-----------------------|---------------|----------|--|--|

|                         | Unattended G                 | uest OS Insta                                                                                                                                                                                                                     | ll Setu       | р                    |                       |               |          |  |  |

|                         | Additionally you can en      | You can configure the unattended guest OS install by modifying username, password, and hostname.<br>Additionally you can enable guest additions install. For Microsoft Windows guests it is possible to<br>provide a product key. |               |                      |                       |               |          |  |  |

|                         | Username and Password        | d                                                                                                                                                                                                                                 |               | Additional Options   |                       |               |          |  |  |

|                         |                              |                                                                                                                                                                                                                                   |               |                      |                       |               |          |  |  |

|                         | U <u>s</u> ername:           | Jthater                                                                                                                                                                                                                           | •             |                      |                       | _             |          |  |  |

|                         | Pass <u>w</u> ord:           | Password123                                                                                                                                                                                                                       |               |                      | Ubuntu_Example        |               | 2        |  |  |

|                         | Repeat Password:             | Password123                                                                                                                                                                                                                       |               | <u>D</u> omain Name: | myguest.virtualbox.o  | rg            |          |  |  |

|                         |                              | 10334010125                                                                                                                                                                                                                       |               |                      | Install in Background | ł             |          |  |  |

|                         | ✓ Guest Additions            |                                                                                                                                                                                                                                   |               |                      |                       |               |          |  |  |

|                         | Guest <u>A</u> dditions ISO: | C:\Program Files                                                                                                                                                                                                                  | \Oracle\Virtu | ualBox\VBoxGuestAd   | lditions.iso          |               |          |  |  |

| Help                    |                              |                                                                                                                                                                                                                                   |               | <u>B</u> ack         | <u>N</u> ext          | <u>C</u> ance | el       |  |  |

Figure 4: VM User Setup

Once you click next, you will be greeted with resource allocation. This is gonna be up to your system, but it is recommended to allocate around 8GB of RAM and 4 CPUs. However, it is more important to stay within the green so that your host machine will still be stable. This is what my settings look like.

| 🦸 Create Virtual Mach | ine                                                                                                                                                                                      | ?       | × |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---|

| Create Virtual Mach   | Hardware<br>You can modify virtual machine's hardware by changing amount of RAM and virtual CPU count.<br>Enabling EFI is also possible.<br>Base Memory:<br>4 MB 16384 MB<br>Processors: | 8000 MB |   |

|                       |                                                                                                                                                                                          |         |   |

Figure 5: VM Hardware Allocation

Once you click next, you will be greeted with setting up the virtual hard disk. For the environment that will be set up, I would recommend **a minimum of 75 GB**, but depending on what you end up doing, you may want up to 120 GB allocated. For this example, I am allocating 100 GB of space. You may also opt to pre-allocate the full size, but I leave this setting turned off.

| 🦸 Create Virtual Machine | e                                                                                                                                                                                                                 | ?            | ×     |  |  |  |  |  |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|--|--|--|--|--|

| antillion .              | Virtual Hard disk                                                                                                                                                                                                 |              |       |  |  |  |  |  |

|                          | If you wish you can add a virtual hard disk to the new machine. You can either create a new hard disk file or select an existing one. Alternatively you can create a virtual machine without a virtual hard disk. |              |       |  |  |  |  |  |

|                          | <u>C</u> reate a Virtual Hard Disk Now                                                                                                                                                                            |              |       |  |  |  |  |  |

|                          | Disk Size:                                                                                                                                                                                                        | 100.0        | DO GB |  |  |  |  |  |

|                          | 4.00 MB 2.00 TB                                                                                                                                                                                                   |              |       |  |  |  |  |  |

|                          | Pre-allocate <u>F</u> ull Size                                                                                                                                                                                    |              |       |  |  |  |  |  |

|                          | U <u>s</u> e an Existing Virtual Hard Disk File                                                                                                                                                                   |              |       |  |  |  |  |  |

|                          | 🔀 Ubuntu 22.10.vdi (Normal, 120.09 GB)                                                                                                                                                                            |              |       |  |  |  |  |  |

|                          | Do Not Add a Virtual Hard Disk                                                                                                                                                                                    |              |       |  |  |  |  |  |

|                          |                                                                                                                                                                                                                   |              |       |  |  |  |  |  |

|                          |                                                                                                                                                                                                                   |              |       |  |  |  |  |  |

|                          |                                                                                                                                                                                                                   |              |       |  |  |  |  |  |

| Help                     | <u>B</u> ack <u>N</u> ext                                                                                                                                                                                         | <u>C</u> ano | el    |  |  |  |  |  |

Figure 6: VM Hard Disk Allocation

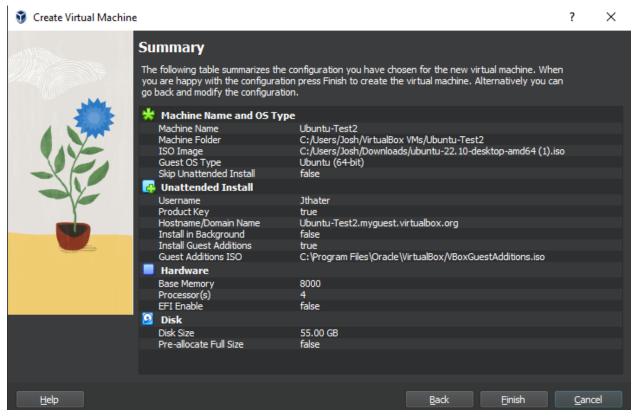

Once all of that is done, you will see a summary page. Ensure that everything is set up correctly, and click "Finish."

Figure 7: VM Setup Summary

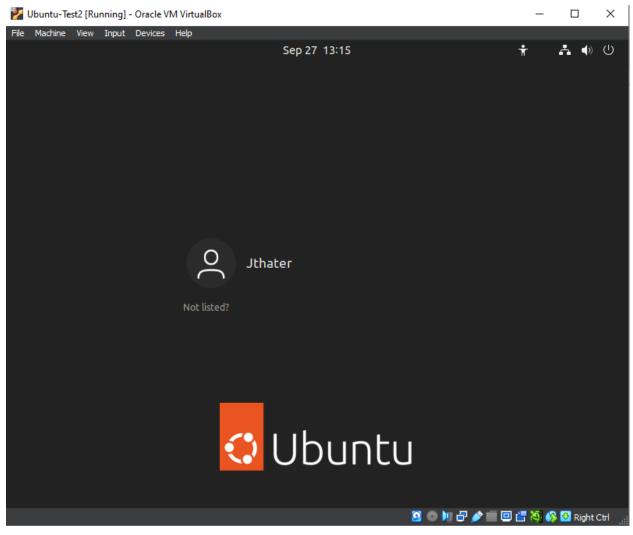

Once you hit "Finish", Virtual Box will start running the machine and will begin downloading the ISO. It will take a few minutes to get everything fully set up. Once it is done downloading, it should kick you to a login screen. It should look something like this:

Figure 8: VM Setup Login

Go ahead and log in with your password. The last step is to ensure that the guest additions are downloaded correctly. Go full screen, and if the virtual machine also goes full screen, that means the guest additions have downloaded correctly! (NOTE: It seems that the virtual machine will not go full screen on 1440p monitors, only 1080p and smaller resolutions). With all of this done, you have successfully set up the virtual machine environment!

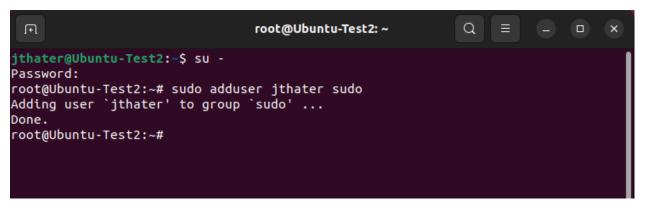

Also note, for some reason, sometimes you will not be added to the "sudoers" file. There are many ways to add yourself to this file, but I will outline a way that worked for me.

- Open up the terminal and type: su -

- Enter your password

- Type: sudo adduser [your username] sudo

If you did this correctly, you should see a message that you have been added to group sudo. Your terminal should look something like the figure below.

Figure 9: VM Sudo Setup

You can test if this worked by exiting out of the terminal, opening it back up, and typing something like "sudo ls." If you don't get an error, then you have successfully added yourself to the sudo group and can run commands as root.

# NOTE: you may have to reboot the system to see the change go into effect (power off the machine).

# Guide to Setting up Tool Environment for Analog Design Flow

Now that you have set up your virtual machine environment, it is time to begin downloading the tools needed for the analog design flow. It should be noted that since this whole process is still essentially in "alpha," things are changing quite a bit, so by the time you read this, some of this information may be outdated. I recommend future teams to update this information as it changes.

This part of the guide will just give a brief overview of the tools and how to install them; it will not go in-depth about their use and how to use them to go through the analog process flow. This information can be found in the next section of this document.

# One last reminder that the rest of this guide is written assuming you are using an Ubuntu system. If you are not running an Ubuntu system, then you will have to figure out how to run these commands on your own system.

Before starting to download things, it is probably a good idea to update/upgrade your *"apt-get"* command as it may not be the most recent after a new download of a virtual machine. To do this, run the commands:

- sudo apt-get update

- sudo apt-get upgrade

If you run these commands and they give you errors, look up the error numbers you are getting, but it most likely means that you are running an outdated version of Ubuntu and need to upgrade your machine. I won't go into that here, but there are plenty of guides on how to do this.

Once these commands are run, you should have no problem using "*sudo apt-get install [xxx]*" to download packages and dependencies for these tools.

## **Required Packages**

In this section, I will list out some needed/useful packages that you will want to download for your use in this environment. These packages are not dependencies for the software you will be downloading, but they are helpful to have as you work. The first package you will need is the Git package. This will allow you to clone repositories, which is vital for installing some of the software. To install Git, simply type this command in the terminal:

#### • sudo apt-get install git

The next package you want to install is some type of text editor that will allow you to read and edit files within Linux. There are many text editors to choose from, but I recommend Vim. To install Vim, simply type the following command:

• sudo apt-get install vim

## Magic VLSI

The first tool that you want to download and configure will be a tool called Magic VLSI. This tool is essential for creating a lot of libraries and will have you download many of the dependencies that will be needed for other tools. Magic will be a tool that you can use for your layouts and to perform device extractions for LVS and post-layout parasitics. It can also generate GDS and LEF files.

Documentation of Magic can be found here: http://opencircuitdesign.com/magic/index.html

This is the page that has all the information you would want to know about Magic, so look around.

In order to install Magic, navigate to the install page. Here, you will find instructions on the dependencies, configurations, and setup of this tool. For the sake of simplicity, I will list all of the dependencies and the commands to get them for an Ubuntu system. Some of these dependencies are optional, depending on how you want to configure Magic. However, I recommend getting all of them because they do not take up much space, and some of the other software will need these dependencies installed anyway. These dependencies and commands to get them are as follows:

- sudo apt-get install m4

- sudo apt-get install tcsh

- sudo apt-get install csh

- sudo apt-get install libx11-dev

- sudo apt-get install tcl-dev tk-dev

- sudo apt-get install libcairo2-dev

Optional:

- sudo apt-get install mesa-common-dev libglu1-mesa-dev

- sudo apt-get install libncurses-dev

NOTE: You can download all of these dependencies at once by typing them all in a single line. Such as:

• Sudo apt-get install m4 tcsh csh libx11-dev tcl-dev tk-dev libcairo2-dev

Once you have all of the dependencies downloaded successfully, you should be able to compile and install Magic successfully. I recommend installing it from the GitHub repository as it contains the most recent version. To do this, simply clone the git repository using the command:

- git clone https://github.com/RTimothyEdwards/magic

- Is

This will clone the GitHub repository into a directory on your virtual machine. This directory should show up in your current directory. You should be able to run the *"Is"* command to see it. The figure below illustrates this cloning and where the repository got cloned.

```

jthater@Ubuntu-Example:~$ git clone https://github.com/RTimothyEdwards/magic

Cloning into 'magic'...

remote: Enumerating objects: 12009, done.

remote: Counting objects: 100% (2069/2069), done.

remote: Compressing objects: 100% (887/887), done.

remote: Total 12009 (delta 1174), reused 1903 (delta 1030), pack-reused 9940

Receiving objects: 100% (12009/12009), 9.88 MiB | 25.48 MiB/s, done.

Resolving deltas: 100% (7390/7390), done.

jthater@Ubuntu-Example:~$ ls

Desktop Downloads Music Public Templates

Documents magic Pictures snap Videos

jthater@Ubuntu-Example:~$

```

Figure 10: Magic Reposistory Cloned

Once you have confirmed that you have cloned the Magic repository successfully, simply move into the directory using *"cd"*. *I.e.:*

• cd magic

Doing this will move you into the Magic directory, and from here, you can manually configure and install Magic. To configure Magic, simply type the following commands:

- ./configure --enable-cairo-offscreen

- make

- sudo make install

With this specific configuration it should help to alleviate any glitches that may occur with the software when using the OpenGL graphics interface if you choose to use it (read more about this in the Magic documentation).

It should be noted that the default path for the installation places all of the files in the directory /usr/local/bin/magic.

Once this is done, you can verify that you have installed Magic successfully by simply typing *"magic"* into the console. You should see the Magic tool come up, and you should be able to navigate around it. The figure below shows what you should be seeing.

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 | layout1                                                            |       | ×                       |

|------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------|-------|-------------------------|

| File | Edit                                         | Cell Window                                                                                                                                           | Layers I                                                                                                                 | Orc Options                                                                                                               | DRC                                                             | Loaded: (UNNAMED) Editing: (UNNAMED) Tool: box Technology: minimum |       | (-16 +7) -16 +7 microns |

| 1    |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       | _                       |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 | tkcon 2.3 Main                                                     | - • × |                         |

|      | E                                            | ile <u>C</u> onsole <u>E</u>                                                                                                                          | dit <u>I</u> nterp                                                                                                       | <u>P</u> refs <u>H</u> isto                                                                                               | ory <u>H</u> elp                                                |                                                                    |       |                         |

|      |                                              |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 | ayout window                                                       | 1     | 2                       |

|      | US                                           | e closewrappe                                                                                                                                         | er to remo                                                                                                               | ove a new G                                                                                                               | UI-based                                                        | layout window                                                      |       |                         |

|      | Ma                                           |                                                                                                                                                       |                                                                                                                          |                                                                                                                           |                                                                 |                                                                    |       |                         |

|      | 110                                          | igic 8.3 revis                                                                                                                                        | sion 436 -                                                                                                               | Compiled                                                                                                                  | on Tue Oc                                                       | t 3 11:41:58 PM CDT 2023.                                          |       | 1                       |

|      | St                                           | arting magic                                                                                                                                          | under Tcl                                                                                                                | Compiled<br>interpret                                                                                                     | on Tue Oc<br>er                                                 | t 3 11:41:58 PM CDT 2023.                                          |       | ž                       |

|      | St<br>Us<br>Us                               | arting magic<br>ing Tk conso<br>ing TrueColo                                                                                                          | under Tcl<br>le window<br>r, Visuall                                                                                     | . interpret<br>D 0x23 dep                                                                                                 | er                                                              | t 3 11:41:58 PM CDT 2023.                                          |       |                         |

|      | St<br>Us<br>Us<br>Pr                         | arting magic<br>ing Tk conso<br>ing TrueColo<br>ocessing sys                                                                                          | under Tcl<br>le window<br>r, Visuall<br>tem .magio                                                                       | . interpret<br>D 0x23 dep<br>crc file                                                                                     | er<br>th 24                                                     | t 3 11:41:58 PM CDT 2023.                                          |       | 8                       |

|      | St<br>Us<br>Us<br>Pr<br>Ne                   | arting magic<br>ing Tk conso<br>ing TrueColo                                                                                                          | under Tcl<br>le window<br>r, Visuall<br>tem .magic<br>ll not hav                                                         | . interpret<br>D 0x23 dep<br>crc file<br>ve a title                                                                       | er<br>th 24<br>caption.                                         | t 3 11:41:58 PM CDT 2023.                                          |       |                         |

|      | St<br>Us<br>Pr<br>Ne<br>Ne<br>Ne             | arting magic<br>ing Tk conso<br>ing TrueColo<br>ocessing sys<br>w windows wi<br>w windows wi<br>w windows wi                                          | under Tcl<br>le window<br>r, Visuall<br>tem .magic<br>ll not hay<br>ll not hay<br>ll not hay                             | . interpret<br>D 0x23 dep<br>crc file<br>ve a title<br>ve scroll b<br>ve a border                                         | er<br>th 24<br>caption.<br>ars.                                 |                                                                    |       |                         |

|      | St<br>Us<br>Pr<br>Ne<br>Ne<br>Re             | arting magic<br>ing Tk conso<br>ing TrueColo<br>ocessing sys<br>w windows wi<br>w windows wi<br>w windows wi<br>painting com                          | under Tcl<br>le window<br>r, Visuall<br>tem .magic<br>ll not hav<br>ll not hav<br>ll not hav<br>sole in ma               | interpret<br>D 0x23 dep<br>crc file<br>ve a title<br>ve scroll b<br>ve a border<br>agic layout                            | er<br>th 24<br>caption.<br>ars.<br>window c                     |                                                                    |       | 3                       |

|      | St<br>Us<br>Vr<br>Ne<br>Ne<br>Re<br>Us       | arting magic<br>ing Tk conso<br>ing TrueColor<br>ocessing sys<br>w windows wi<br>w windows wi<br>w windows wi<br>painting cons<br>ing technolog       | under Tcl<br>le window<br>r, Visuall<br>tem .magic<br>ll not hav<br>ll not hav<br>ll not hav<br>sole in ma               | interpret<br>D 0x23 dep<br>crc file<br>ve a title<br>ve scroll b<br>ve a border<br>agic layout                            | er<br>th 24<br>caption.<br>ars.<br>window c                     |                                                                    |       | 3                       |

|      | St<br>Us<br>Us<br>Pr<br>Ne<br>Ne<br>Re<br>Us | arting magic<br>ing Tk conso<br>occessing sys:<br>w windows wi<br>w windows wi<br>painting consol<br>ing technolo<br>ot cell box:                     | under Tcl<br>Le window<br>r, Visuall<br>tem .magic<br>Ll not hav<br>Ll not hav<br>Ll not hav<br>sole in ma<br>gy "minimu | interpret<br>D 0x23 dep<br>rc file<br>ve a title<br>ve a title<br>ve a border<br>agic layout<br>mm", versio               | er<br>th 24<br>caption.<br>ars.<br>window c<br>n 0.0            |                                                                    |       | 3                       |

|      | St<br>Us<br>Pr<br>Ne<br>Re<br>Us<br>Ro       | arting magic<br>ing Tk conso<br>occessing sys<br>w windows wi<br>w windows wi<br>painting cons<br>ing technolog<br>ot cell box:<br>wid                | under Tcl<br>le window<br>r, VisualJ<br>tem .magic<br>ll not hav<br>ll not hav<br>sole in ma<br>gy "minimu<br>th x heigh | interpret<br>D 0x23 dep<br>rer file<br>re a title<br>re scroll b<br>re a border<br>ngic layout<br>mm", versio<br>ht ( llx | er<br>th 24<br>caption.<br>ars.<br>window c<br>n 0.0<br>, lly ) | olors<br>, ( urx, ury ) area (units^2)                             |       | 3                       |

|      | St<br>US<br>Pr<br>Ne<br>Re<br>US<br>Ro<br>mi | arting magic<br>ing Truecolo<br>ocessing syst<br>w windows wi<br>w windows wi<br>painting com-<br>ing technolog<br>ot cell box:<br>wid<br>crons: 1.00 | under Tcl<br>Le window<br>r, Visuall<br>tem .magic<br>Ll not hav<br>Ll not hav<br>Ll not hav<br>sole in ma<br>gy "minimu | interpret<br>D 0x23 dep<br>rc file<br>ve a title<br>ve a border<br>agic layout<br>mm", versio<br>nt ( llx<br>0 (0.000     | er<br>th 24<br>caption.<br>ars.<br>window c<br>n 0.0<br>, lly ) | olors<br>, ( urx, ury ) area (units^2)<br>, ( 1.000, 1.000) 1.000  |       | 3                       |

Figure 11: Magic Startup Screen

If you are able to open Magic with no issue, then you have successfully installed the software and are ready to move on to the next step.

## Xschem

The next tool that you will be downloading is Xschem. Xschem is a schematic editor that allows you to create schematics, symbols, test benches and will create SPICE netlists for testing. I recommend this over other open-source schematic editors, such as Xcircuit, because it feels and operates closer to commercial-grade tools (like Cadence).

Documentation for Xschem can be found here: https://xschem.sourceforge.io/stefan/index.html

Just like with Magic, this page will contain all information about how to install and configure Xschem. The documentation on how to use this software is very in-depth, so I <u>highly</u> <u>recommend</u> going through and reading the documentation once you get everything set up.

This software also requires some dependencies to be installed, but luckily, most of them have already been installed when Magic was installed, so only a few more need to be added. To get the rest of the dependencies, simply type:

- sudo apt-get install flex

- sudo apt-get install bison

- sudo apt-get install libxpm-dev

With all of these dependencies installed, Xschem can now be configured and installed. If you are following this guide section by section, then make sure you are back in your home directory before running this next step. This can simply be done with:

- cd

- This will move you back to your home directory and should be done each time you begin installing new software

Now, simply clone this repository using the command:

• git clone https://github.com/StefanSchippers/xschem

Just like with Magic, if you did everything properly, you should be able to *"Is"* and see the Xschem directory. To install this software, simply type the commands from your home directory:

- cd xschem

- ./configure

- make

- sudo make install

The default installation path of this software should be /usr/local/bin/xschem. NOTE: You can change this default directory when you run the "./configure" command if you so choose.

To ensure that everything is installed correctly, simply type the command *"xschem"* into the terminal, and you should be greeted with a similar-looking screen, as seen in the figure below.

|           |      |       |       | ,         | enocen | woodiic  |      | xschem  | n - untit | led.sch |        |          | $\sim$    |                               |          |         |       | ×          |

|-----------|------|-------|-------|-----------|--------|----------|------|---------|-----------|---------|--------|----------|-----------|-------------------------------|----------|---------|-------|------------|

| File Edi  | t Op | tions | View  | Propertie | s Laye | rs Tools | Symb | ol High | light Si  | mulatio | า      |          |           | Netl                          | ist Sim  | ulate V | Vaves | Help       |

|           |      |       |       | ]; i'i ×  |        |          |      |         |           |         |        | 27       | <u> </u>  | , <sup>K</sup> 2 <sup>3</sup> | •        |         | +≣ ►  | <u>است</u> |

| untitled. |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

|           |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

| e<br>e    |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

|           |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

| (         |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

| t .       |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

|           |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

| č ·       |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

| i         |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

| :         |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

| t<br>I    |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

| t .       |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

| (         |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

|           |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

|           |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

|           |      |       |       |           |        |          |      |         |           |         |        |          |           |                               |          |         |       |            |

| SNAP: 10  | )    |       | GRID: | 20        | NE     | TLIST MO | DDE: | spice   | NUM L     | OCK SET | l mous | se = -90 | 0 100 - s | elected                       | : 0 path | n: .    |       |            |

Figure 12: Xschem Startup Screen

If you see this screen, then you have successfully installed Xschem and are ready to move on to the next step.

## **Ngspice**

The next tool that you will install is Ngspice. Ngspice is an analog/mixed-signal simulation tool. This will allow you to read in SPICE netlists (and, with more recent versions, more complex netlists) and run different types of circuit analysis on them, such as DC sweeps, transient simulations, AC tests, and many, many more. It also allows you to simulate digital design through Xspice, which is installed as part of this software.

The Ngspice documentation can be found here: https://ngspice.sourceforge.io/

To get a fully featured Ngspice, there are a few dependencies that you must download. They include:

- sudo apt-get install libxaw7-dev

- sudo apt-get install lib64readline8 libreadline-dev

- It should be noted that this dependency can be very finicky, so you may have to change the 64 to a 32, or there might be a new version, so you might need to change the 8 to a 9. I wouldn't worry too much if you can't get this to work, as it is highly unlikely that you will use readlines for Ngspice for anything that you will work on.

You can download the Ngspice software from a Git repository like the other software, but this is more complicated than downloading it from a tar file in this case. So, I would recommend downloading this software from the tar file found here:

https://sourceforge.net/projects/ngspice/files/ng-spice-rework/41/

Download that tar file and navigate to the downloads file from the terminal. This can be achieved by being in your home directory and typing the command

#### cd Downloads

Once in this directory, type "Is", and you should see a file named "ngspice-41.tar.gz" or something similar. Once you have confirmed the file is there, type the following command to unzip the file.

#### • tar -xvzf ngspice-41.tar.gz

If you've done everything correctly, it should look something like the figure below.

```

jthater@Ubuntu-Example:~$ cd Downloads/

jthater@Ubuntu-Example:~/Downloads$ ls

ngspice-41.tar.gz

jthater@Ubuntu-Example:~/Downloads$ tar -xvzf ngspice-41.tar.gz

ngspice-41/

```

#### Figure 13: Unzipped Ngspice File

Unzipping the file will result in a bunch of lines being output to the terminal. Once everything is done, I recommend moving the file into your home directory. This can be done with the command:

• mv ngspice-41 ..

If done correctly, you can navigate back to your home directory, and you should be able to use *"Is"* to see it. Once you have confirmed that the file is there, you can run the following commands:

- cd ngspice-41

- mkdir release

- cd release

- ../configure --with-x --enable-xspice --disable-debug --enable-cider

--with-readlines=yes --enable-predictor --enable-osdi --enable-openmp

- Must configure with osdi in order to support ReRAM simulations using Ngspice

- make 2>&1 | tee make.log

- sudo make install

Running these commands will take longer than any of the setups for the other software, so be prepared to wait a few minutes for this installation. To ensure that the download has been successful, simply type *"ngspice"* into the terminal. If you do so, you should see something similar to the figure seen below.

```

jthater@Ubuntu-Example:~$ ngspice

******

** ngspice-41 : Circuit level simulation program

** The U. C. Berkeley CAD Group

** Copyright 1985-1994, Regents of the University of California.

** Copyright 2001-2023, The ngspice team.

** Please get your ngspice manual from https://ngspice.sourceforge.io/docs.html

** Please file your bug-reports at http://ngspice.sourceforge.net/bugrep.html

** Creation Date: Wed Oct 4 06:54:37 UTC 2023

******

ngspice 2 ->

```

Figure 14: Ngspice Startup Screen

If you see something similar to this screen, then you have successfully installed Ngspice and are ready to move on to the next software.

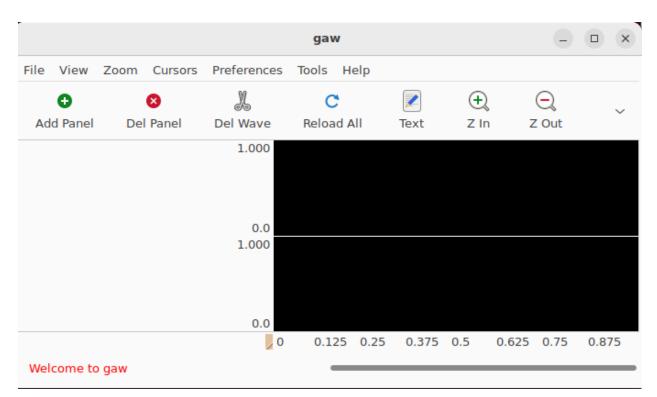

## **GAW** (optional)

GAW is a way to view the waveforms that are generated from Xschem. There are many options to view waveforms, including through Xschem directly, through Ngspice, or other waveform viewers. I recommend looking up waveform viewers yourself and finding something that fits your needs. I only include GAW since it is the one that I have worked with and am used to.

To download GAW, go here and download the latest version: <u>https://download.tuxfamily.org/gaw/download/</u>

To download GAW, you will need this dependency:

#### • sudo apt-get install libgtk-3-dev

Optional:

- sudo apt-get install xterm

- This is an emulator that will allow a Ngspice terminal to open when doing simulations in Xschem. This will allow you to use Ngpsice to view waveforms. I recommend installing this as well.

Then, from your home directory, enter the following commands:

- cd Downloads

- tar -xvzf gaw3-20220315.tar.gz

- mv gaw3-20220315 ..

- cd

- cd gaw3-20220315

- ./configure

- make

- sudo make install

To confirm that GAW has been installed correctly, type gaw into the terminal, and you should see something similar to the figure below pop up.

Figure 15: GAW Startup Screen

## Netgen

The next tool that must be installed is Netgen. Netgen is a tool that will be able to perform LVS on two netlists, whether it be SPICE or Verilog.

Documentation for Netgen can be found here: http://opencircuitdesign.com/netgen/index.html

This documentation page is much like Magic (as it is made by the same person). There are guides on how to install this software, and there are some tutorials on how to use the software. It's a good idea to look around in the "Tutorials" and "References" pages for very detailed information about all of the different things Netgen can do.

The installation of Netgen is very simple. Make sure you are in your home directory before performing this next command. Simply copy the Netgen GitHub repository using the command:

• git clone <u>https://github.com/RTimothyEdwards/netgen</u>

Once you have successfully cloned the repository, enter into the Netgen directory and run the following commands.

- ./configure

- make

- sudo make install

If you have successfully installed Netgen, then simply type *"netgen"* into the terminal, and you should see something similar to what is shown below.

| tkcon 2.3 Main                                                                                                                                                                                                                                                                                                         | - 0 | × |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|

| <u>F</u> ile <u>Console</u> <u>E</u> dit <u>Interp</u> <u>P</u> refs <u>H</u> istory <u>H</u> elp                                                                                                                                                                                                                      |     |   |

| Running NetGen Console Functions<br>Netgen 1.5.259 compiled on Wed Oct 4 01:46:02 PM CDT 2023<br>Warning: netgen command 'format' use fully-qualified name '::netgen::<br>Warning: netgen command 'global' use fully-qualified name '::netgen::<br>Main console display active (Tcl8.6.12 / Tk8.6.12)<br>(jthater) 1 % |     |   |

Figure 16: Netgen Startup Screen

Once you have verified that you have installed Netgen, you are ready to move on. If you are planning on doing simple analog designs, then you can most likely stop installing software here and move on to the Open PDKs Install section. The next two software are optional.

### **Open PDKs Install**

The next install is the PDK that you will be designing devices with. As mentioned earlier, the installation will be done through Open PDKs as it has simplified the process of configuring the PDK for open-source tools and files. All you have to do is clone the repository, configure your installation for whichever PDK you want to download - SkyWater or GF180 MCU - and install the files, cells, and ruleset for that PDK. For this installation, I will be assuming that you are installing the SkyWater 130 nm PDK.

Documentation for Open PDKs can be found here: <a href="http://opencircuitdesign.com/open\_pdks/">http://opencircuitdesign.com/open\_pdks/</a>

Clicking through the different tabs will walk you through configurations and installation steps for your respective PDK. This page, however, does not contain much information about the specific PDK you are downloading (like the different cells, rules, etc.).

To find this information, navigate to the documentation for the SkyWater 130 nm process, which can be found here:

https://skywater-pdk.readthedocs.io/en/main/

I heavily recommend reading through some of the documentation for the SkyWater 130 nm PDK, so you get an idea of what you are downloading and the different cells and primitive devices that are available to you.

Once you have read through a little bit of the documentation, you can download and install Open PDKs. This will operate much in the same way as all of the other installations from the source code in GitHub. However, this install has many different configurations depending on which libraries from the PDK you want installed or not. Looking through both the SkyWater documentation as well as the install page on Open Circuit design should show you how to specifically configure these installs for you. It should be noted that you can always add libraries later if you find out you need something from them.

For most general users, the standard build of the SkyWater 130 nm PDK should be fine. To do this, simply type this into the terminal. <u>NOTES: For this install, you need to have Magic and all of the dependencies installed. This is also a very large install, so make sure you have plenty of disk space available. As this is a large download, it will take quite some time, so be patient.</u>

- git clone <a href="https://github.com/RTimothyEdwards/open\_pdks">https://github.com/RTimothyEdwards/open\_pdks</a>

- cd open\_pdks

- ./configure --enable-sky130-pdk --enable-sram-sky130

- make

- sudo make install

- make distclean

While installing this massive script, you may see some warning and errors that pop up throughout the installation process - this is normal. The only thing you need to worry about is if, after going through any of these steps, you encounter "Error 2". If you see this, then something went wrong, and it will direct you to a logfile where you can see what went wrong.

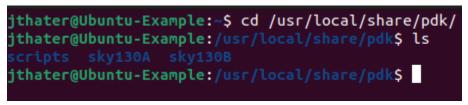

Once you have gone through this installation process, you can check if everything is installed correctly by using the commands shown below to navigate to the pdk installation to view the files:

- cd /usr/local/share/pdk

- Is

If you do this, you should see something similar to the figure below.

Figure 17: Open PDKs File Directory

If you see this, then it is likely that everything was installed correctly. You may notice that there are two Sky130 directories. One is "A" and the other is "B". You don't need to know all about the minute differences between these two. The only difference that matters is that the "sky130A" is the standard process, and the "sky130B" is a modified process that supports the manufacturing of ReRAM. So, if you plan to use ReRAM in any part of your design, you must use the sky130B process for all of your designs. Otherwise, if you have no plans to use ReRAM, then you can go ahead and use the standard sky130A process.

It is a good idea to move into these files and look around to see all that was downloaded. Each directory will contain a libs.ref and a libs.tech directory. The libs.ref directory houses all of the libraries that were downloaded and contains the files for the cells contained in these libraries (read the SkyWater 130 nm PDK documentation for more information about these libraries). The libs.tech directory will house important files for analog design and configuration of the tools for the SkyWater process. This will be covered in the next section of this guide.

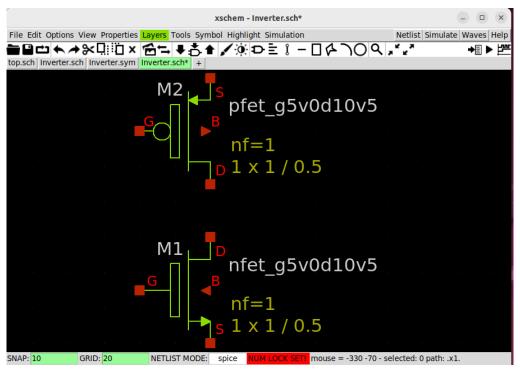

# Tool Usage + Example "Hello World" Type Project

In this part of the guide, I will cover how to use the tools in the analog process flow. Along the way, I will try to link out to videos/documentation that are helpful. I will also include a basic "hello world" type project - which will just be a basic inverter. I will take this inverter through the analog process flow of schematic creation, testbench creation, simulation, netlist extraction for layout, layout, DRC/LVS, post-layout netlist extraction, and finally, post-layout simulation. I will be using the sky130B process variant to design this inverter.

First things first, before proceeding into design, there are a few things to set up still. The first is to create your project directory. This project directory will contain all files relevant to your project. A recommended project directory setup would look something like this:

<myProject> caravel/ gds/ mag/ netgen/ xshcem/ docs/ openlane/ verilog/

These different directories will house the different files of your project and will be required for when you submit your project design through Efabless.

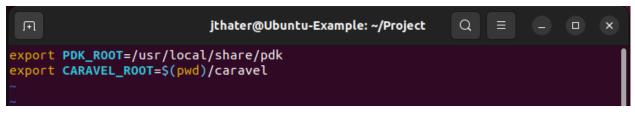

Another thing to set up is global variables. You will need to have these set to successfully use the tools with the SkyWater 130 nm PDK and go through the precheck process that Efabless has. There are many ways to create the global variables, but I will list out the way that I do it (although there is probably a better way to do it). Simply follow these steps:

- cd <myProject>

- touch setup.sh

- vim setup.sh

- This should open up a file called setup.sh. Press *"i"*, which will put you in insert mode and type the following lines in the file:

- export PDK\_ROOT=/usr/local/share/pdk

- This should be the default installation of the SkyWater PDK you downloaded. If you move where these directories were installed, then you need to point this variable where they have been moved to

- export CARAVEL\_ROOT=\$(pwd)/caravel

- Add text here

If you have done this successfully, it should look like the file shown in the figure below.

Figure 18: Setup File for Open-Source Analog Design Flow

Once this is done, press *"ESC"*, on your keyboard, which will place you outside of "insert" mode. Then, in subsequent order, press *":wq"*, which will exit the file while saving the changes you made to it. Then, to make these global variables go into effect, in the terminal type:

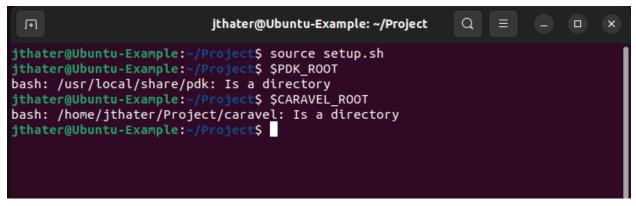

- source setup.sh

- To verify that these global variables were updated, type into the terminal:

- \$PDK\_ROOT

- \$CARAVEL\_ROOT

If you did everything correctly, you should see something like the figure below.

Figure 19: Verification that Global Variables Were Set

This should verify that the global variables have been updated. **NOTE: with the method** outlined here, each time you open up a new terminal window, you will have to run the *"source setup.sh"* code for the global variables to update (which is why I mentioned this way might be inefficient).

With all of this done, you are finally ready to start the open-source analog design flow.

## **Schematic Capture/Creation + Simulation**

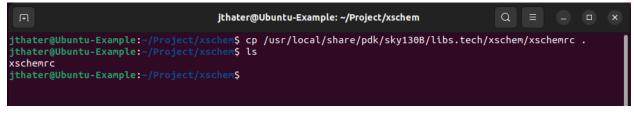

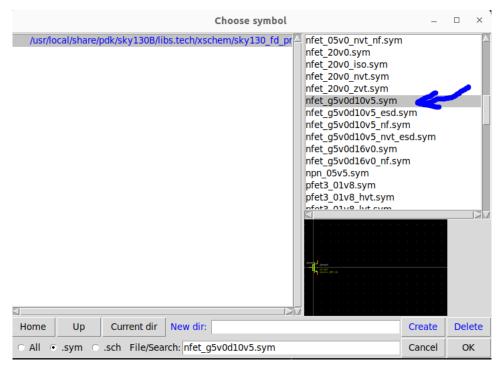

The first step of the analog design flow is schematic/testbench creation. The next step is to simulate your schematic. As these two steps are closely related for the open-source analog design flow, I have decided to put them in the same category. For this guide, I will focus on Xschem for schematic creation. To begin using Xschem to design with the SkyWater 130 nm PDK, you will need to copy the *xschemrc* into your working directory where you plan to your schematics. The *xschemrc* file should be in the xschem directory in the process variant you want to work with (sky130A or sky130B). To copy this file, first, be in the directory where you plan to your plan to work on these schematics, then type:

- cp /usr/local/share/pdk/sky130B/libs.tech/xschem/xschemrc .

- Is

- This verifies that the *xschemr*c file has been properly copied into your current directory.

If you have followed these steps, you should see something similar to the figure below.

Figure 20: Xschemrc File in Folder

Once you have the *xschemrc* file in your working directory, simply type:

xschem

This will open up Xschem into a top-level file for the SkyWater PDK, as seen in the figure below.

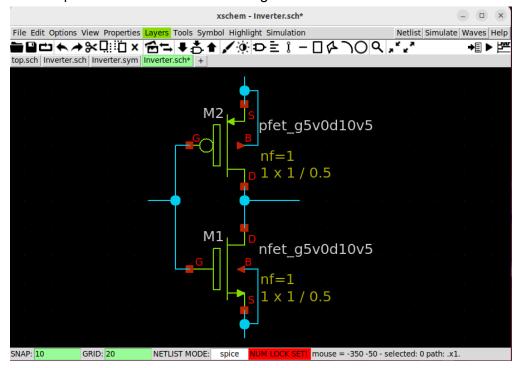

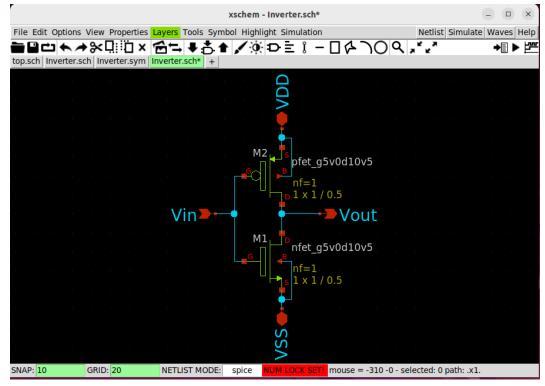

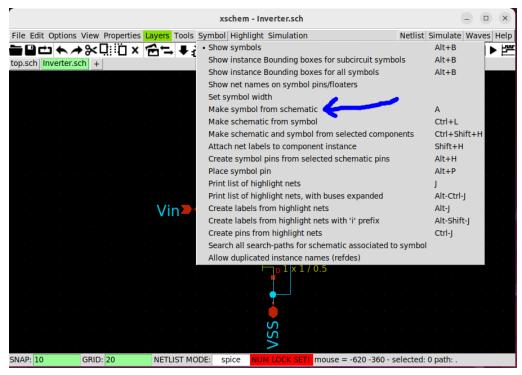

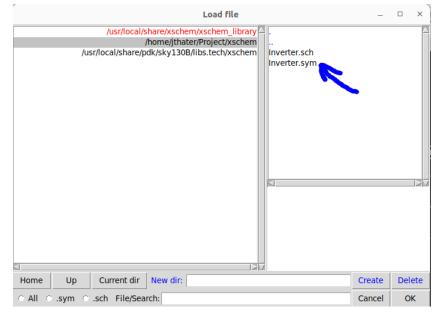

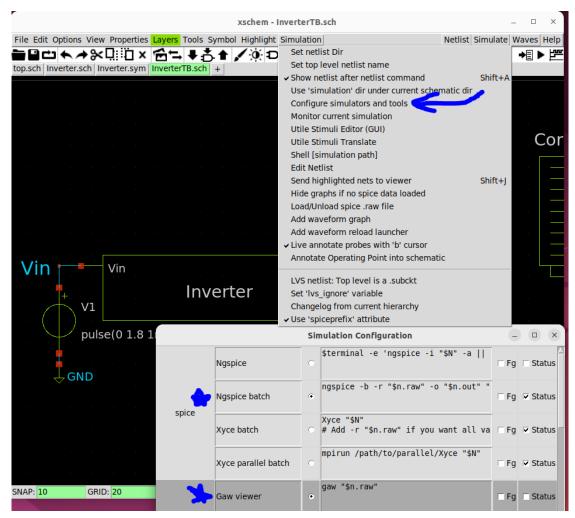

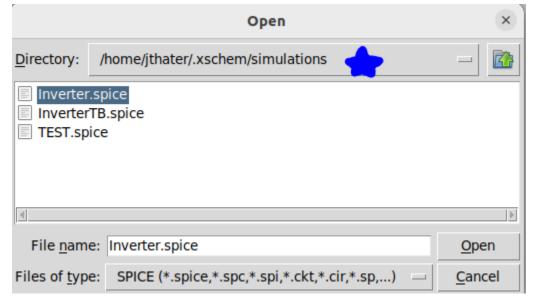

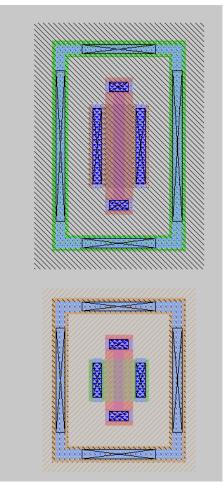

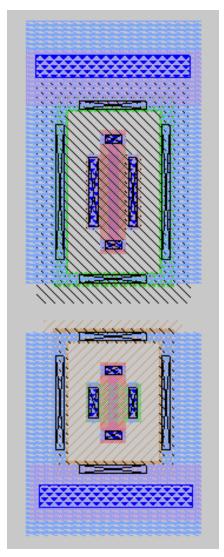

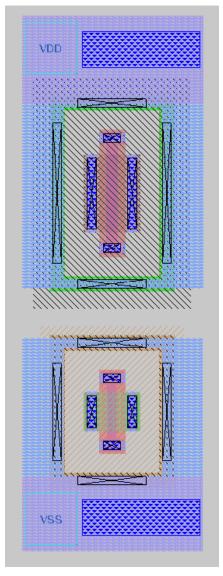

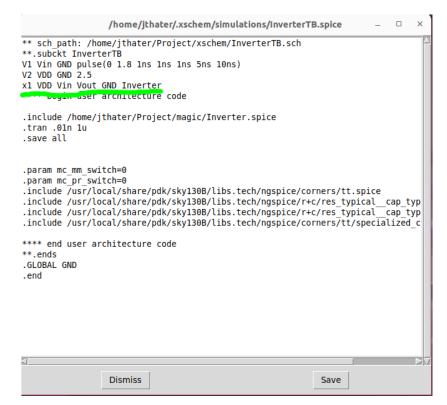

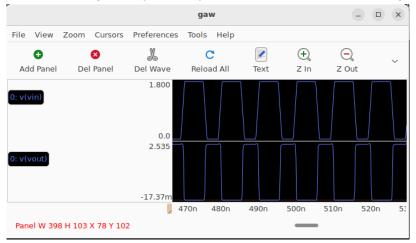

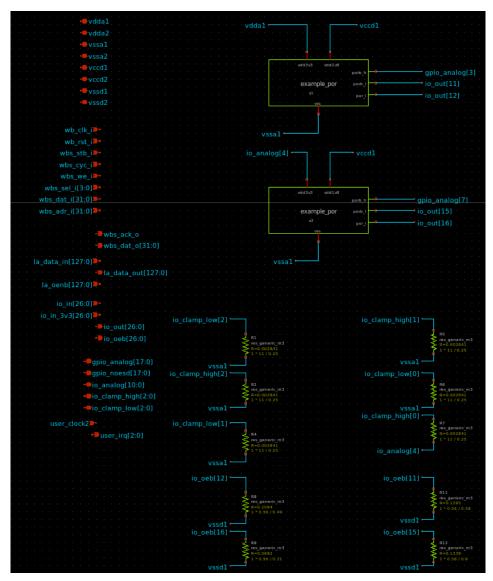

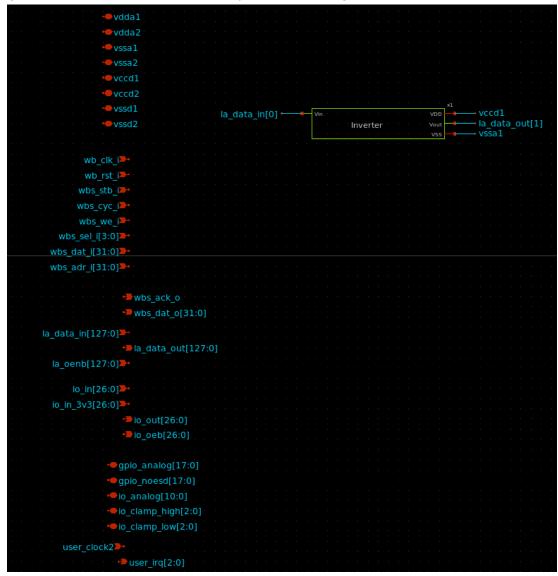

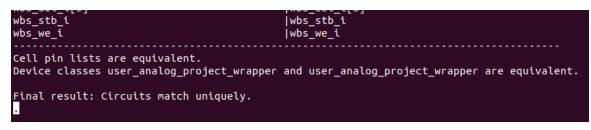

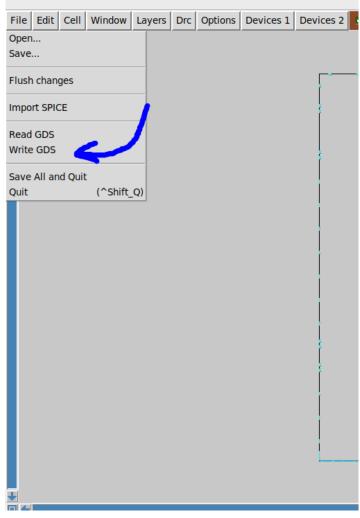

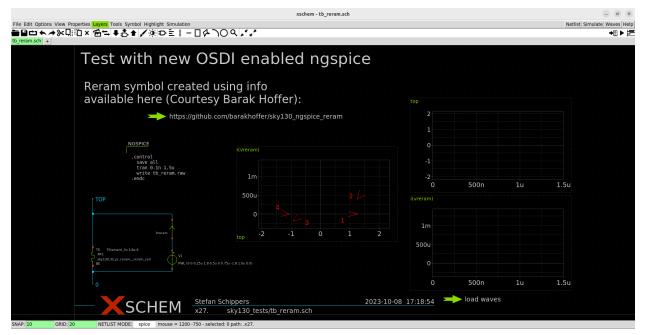

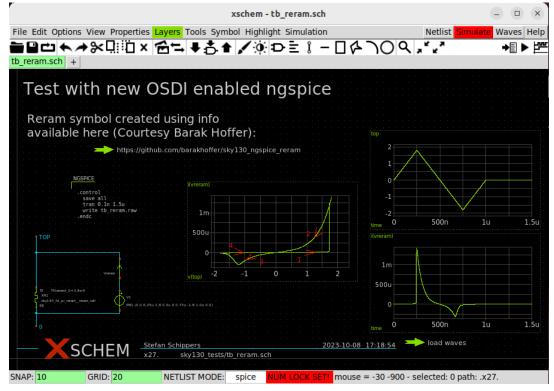

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xschem - top.sch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | - • ×                                                                                  |